Remarque : Pour les hörberts vendus entre octobre 2021 et le 7 février 2022, vous êtes vivement invités à effectuer une mise à jour du firmware immédiate, Voir : https://www.hoerbert.com/firmware

Tous les hörberts après le 7.2.2022 ne sont plus concernés

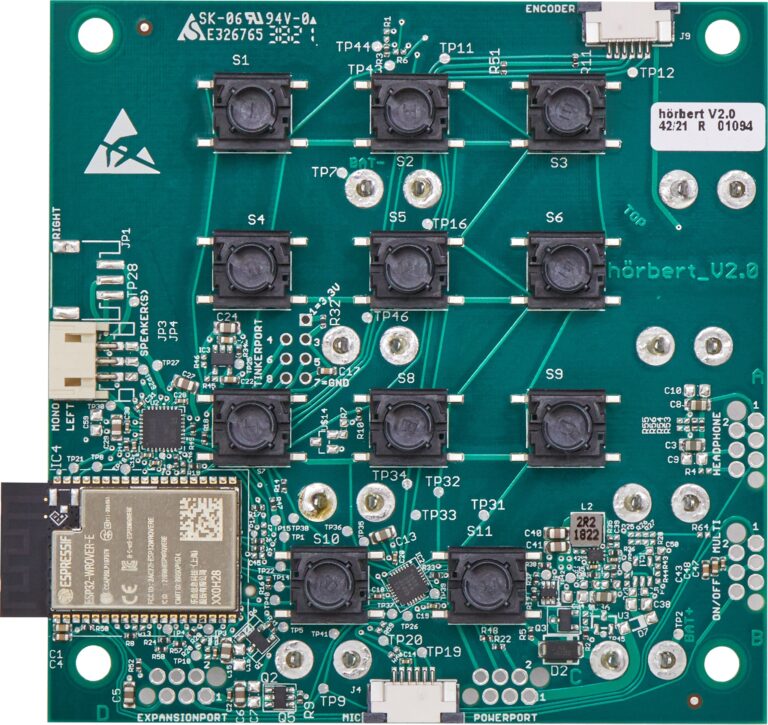

La nouvelle électronique d’hörbert que nous fabriquons depuis octobre 2021, et qui enrichit hörbert de nombreuses nouvelles fonctionnalités, est basée sur un module de processeur très populaire et riche en fonctionnalités. Il s’agit du module WROVER-E de la société Espressif. C’est un module largement utilisé et déployé à des millions d’exemplaires dans le monde entier. Nous utilisons – vous l’aurez deviné – dans hörbert le module avec la plus grande mémoire flash disponible intégrée, pour avoir suffisamment d’espace pour notre micrologiciel – maintenant et à l’avenir.

Exactement comme vous, nous ne pouvons pas voir sur cette carte qu’une erreur sommeille dans le module de processeur, attendant de saboter le module de processeur lui-même.

Malheureusement, il y a une source d’erreur dormant sous le capot de ces modules.

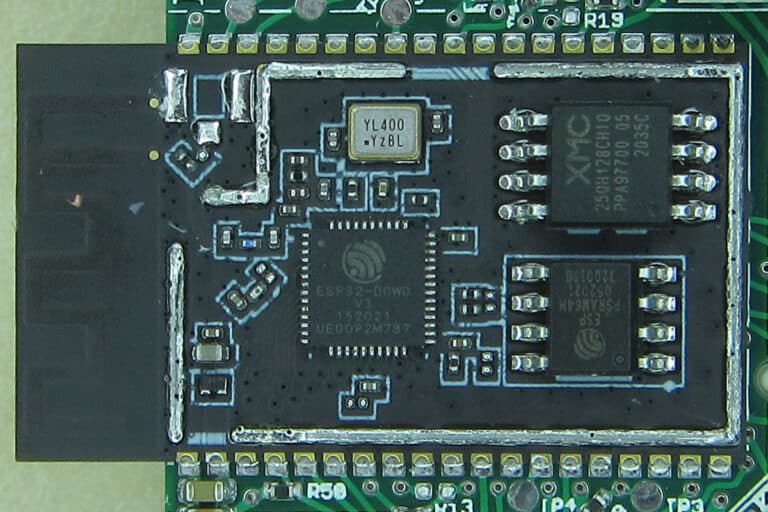

Sur les modules WROVER-E que nous achetons prêts à l’emploi, le processeur et deux puces mémoire sont situés sous le capot métallique de blindage. L’un d’eux est la mémoire flash, sur laquelle le firmware reste stocké même lorsque le module processeur n’a pas de courant.

Comme c’est courant sur le marché, le fabricant installe différentes puces de mémoire flash de tailles et de fonctionnalités différentes provenant de différents fabricants.

Jusque-là, tout est normal.

Tous les chips flash utilisés par Espressif ont des fonctions et des spécifications très similaires.

Une de ces fonctions que de nombreux stockages flash ont est une protection en écriture, que vous pouvez activer à l’aide de commandes spéciales. Les commandes pour activer la protection en écriture varient entre les produits.

Et la protection en écriture est une partie du problème. Et ce seulement pour l’un des cinq types de chips flash interchangeables.

Dans certains de nos modules WROVER-E, une puce flash de la société XMC est effectivement utilisée. Malheureusement, nous ne pouvons pas savoir dans quels modules et dans combien d’hörberts exactement cette puce fonctionne, car elle fait partie du module de processeur que nous ne fabriquons pas nous-mêmes. Dans notre cas, il s’agit de la puce XM25QH128C. (->Fiche technique)

En raison d’une cause inconnue, qu’Espressif n’a malheureusement pas encore trouvée, il peut arriver que la puce flash reçoive des commandes aléatoires, peut-être même sans signification. Ces commandes modifient complètement la puce flash. Comme la protection en écriture de cette puce flash est malheureusement activée par l’erreur, il devient impossible de l’effacer ou de la sauver en conséquence.

Le véritable problème est que les bits d’état correspondants pour la protection en écriture sont définis de manière irrévocable.

Cela rend la puce inutile pour toutes les opérations ultérieures, et doit être physiquement remplacée par une nouvelle puce par nos soins.

L’équipe de support d’Espressif nous a envoyé une solution sous forme d’un extrait de code que nous avons immédiatement intégré dans un nouveau firmware hörbert. Dommage : La solution ne peut empêcher l’erreur que si elle se produit en amont. Super : La solution empêche l’erreur de se produire.

Comme nous ne connaissons pas la cause de l’erreur (données corrompues ?), mais seulement ses effets (protection en écriture !), notre problème est de prévenir la mise en place de la protection en écriture, et ce de manière permanente ! Nous n’avons pas besoin de cette protection en écriture pour la fonctionnalité de hörbert, c’est pourquoi nous fermons simplement la porte au visage de la source d’erreur.

Donc même si à l’avenir la puce Flash reçoit des commandes aléatoires, elle ne pourra plus se verrouiller d’elle-même.

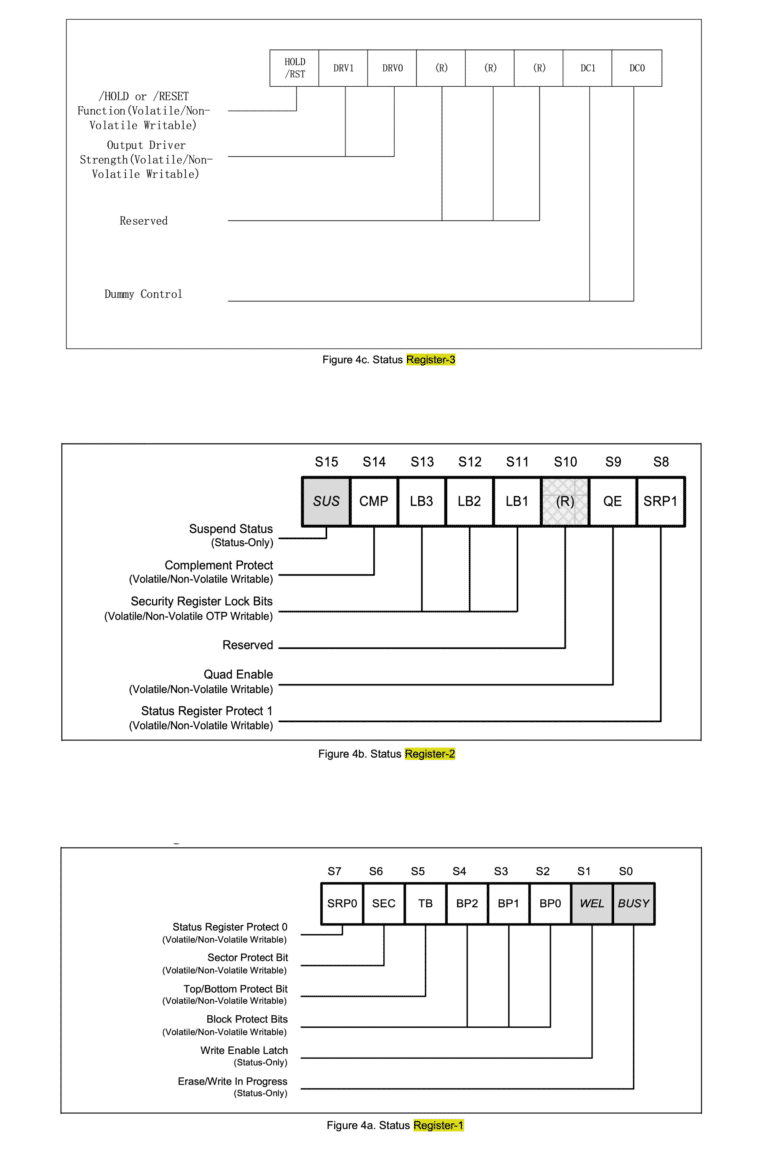

Le chip XM25QH128C est connecté au module WROVER-E via SPI. En plus des commandes d’écriture et de lecture, les trois registres d’état SR1, SR2 et SR3 sur 8 bits peuvent être définis.

Les bits SRP1 (« Status Register Protect 1 ») dans le registre d’état 2 et SRP0 (« Status Register Protect 2 ») dans le registre d’état 1 sont responsables de la protection en écriture.

En configurant ces deux bits sur « 1 », vous empêchez toutes modifications des trois registres d’état pour toujours, car ces bits de protection de registre d’état sont des bits « OTP » (one time programmable). Une fois définis, ils ne peuvent pas être effacés. C’est pourquoi, dans notre nouveau micrologiciel, nous définissons des valeurs raisonnables pour les trois registres d’état dont nous avons besoin pour notre hörbert, puis nous définissons les deux bits de protection de registre d’état. Cela ne peut être fait qu’une seule fois.

Dans notre cas, nous pouvons définir en toute sécurité les registres sur les valeurs 0x600380. (S1=0x80, S2=0x03, S3=0x60) Ces réglages sont les valeurs correctes pour notre micrologiciel et nos fonctions, et en définissant les bits SRP0 et SRP1, cela restera ainsi.

L’identifiant du chip peut être lu en utilisant esptool.py.

Dans notre cas, c’est le fabricant « 20 » (XMC) et l’identifiant du chip 4018 (Flash 128 Mbit)

> esptool.py flash_id esptool.py v3.1-dev Trouvé 2 ports série Port série /dev/ttyUSB0 Connexion........_ Détection du type de chip... ESP32 Le chip est ESP32-D0WD-V3 (révision 3) Fonctionnalités: WiFi, BT, Double cœur, 240MHz, Calibration VRef en efuse, Aucun schéma de codage Le cristal est à 40MHz MAC: 94:3c:c6:c1:55:e4 Téléverser le brouillon... Exécution du brouillon... Brouillon en cours d'exécution... Fabricant: 20 Dispositif: 4018 Taille de flash détectée: 16MB Réinitialisation matérielle via la broche RTS...

Les registres d’état peuvent également être lus avec esptool.py. Voici un exemple de puce mal configurée avec les valeurs des registres d’état 0xe37bfc (S1=0xfc, S2=0x7b, S3=0xe3)

> esptool.py read_flash_status --bytes 3 esptool.py v3.1-dev Trouvé 2 ports série Port série /dev/ttyUSB0 Connexion... Détection du type de chip... ESP32 Le chip est ESP32-D0WD-V3 (révision 3) Fonctionnalités: WiFi, BT, Double cœur, 240MHz, Calibration VRef en efuse, Aucun schéma de codage Le cristal est à 40MHz MAC: 94:3c:c6:c1:55:e4 Brouillon est déjà en cours d'exécution. Aucun téléversement n'est nécessaire. Valeur de l'état: 0xe37bfc Réinitialisation matérielle via la broche RTS...

ets Jul 29 2019 12:21:46 rst:0x1 (POWERON_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) configsip: 0, SPIWP:0xee clk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00 mode:DIO, clock div:2 load:0x3fff0030,len:380 ho 0 tail 12 room 4 load:0x07800000,len:3378177 ets Jul 29 2019 12:21:46 rst:0x10 (RTCWDT_RTC_RESET),boot:0x33 (SPI_FAST_FLASH_BOOT) configsip: 0, SPIWP:0xee clk_drv:0x00,q_drv:0x00,d_drv:0x00,cs0_drv:0x00,hd_drv:0x00,wp_drv:0x00 mode:DIO, clock div:2 [...]

Avertissement : Ne pas utiliser ce code dans votre projet si vous ne comprenez pas quels bits d’état vous pouvez définir et lesquels non !

Ce code nous a été gracieusement fourni par Espressif comme base pour notre propre correctif de support. Il nécessite l’esp-idf d’Espressif. Il s’exécute en RAM et vérifie d’abord l’ID du flash 0x204018. Ensuite, il lit les registres d’état et combine S2 avec le bit de protection de registre d’état absolument nécessaire SRP1, et définit le bit SRP0, qui constituent ensemble le correctif réel.

#inclure "freertos/FreeRTOS.h" #inclure "freertos/task.h" [...]

Cette méthode est mieux comprise lorsqu’on examine les registres d’état du Flash-Chip.

Vous êtes actuellement en train de consulter le contenu d'un espace réservé de Accessibility Widget. Pour accéder au contenu réel, cliquez sur le bouton ci-dessous. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informationsVous êtes actuellement en train de consulter le contenu d'un espace réservé de Vimeo. Pour accéder au contenu réel, cliquez sur le bouton ci-dessous. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informationsVous êtes actuellement en train de consulter le contenu d'un espace réservé de YouTube. Pour accéder au contenu réel, cliquez sur le bouton ci-dessous. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informationsVous devez charger le contenu de reCAPTCHA pour soumettre le formulaire. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informationsVous êtes actuellement en train de consulter le contenu d'un espace réservé de Google Maps. Pour accéder au contenu réel, cliquez sur le bouton ci-dessous. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informationsVous devez charger le contenu de reCAPTCHA pour soumettre le formulaire. Veuillez noter que ce faisant, des données seront partagées avec des providers tiers.

Plus d'informations